SYNTAX :

COMPONENT <component_name> IS

GENERIC (generic_list);

PORT (port_list);

END COMPONENT <component_name>;

Component Declaration:

A Component should be declared before using it.

Where to Put ?

Should be placed inside architecture block ,before begin statements.

Architecture module1_arch of module1_ent is

-- Component Declaration here--

begin

end module1_arch ;

Component Instantiation or Mapping :

After Declaring the component it should be port mapped.

Where to Put ?

Should be placed inside architecture block ,after begin statements.

Architecture module1_arch of module1_ent is

begin

-- Component Port Mapping here --

end module1_arch ;

Example 1:

entity module1_ent is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

F : out STD_LOGIC );

end module1_ent;

Architecture module1_arch of module1_ent is

-- Component Declaration --

component XOR_2 is

port ( a : in std_logic;

b : in std_logic;

f : out std_logic

);

end component XOR_2;

begin

-- Component Port Mapping --

M1: XOR_2 port map ( A=> a ,B=> b,F=> f);

end module1_arch ;

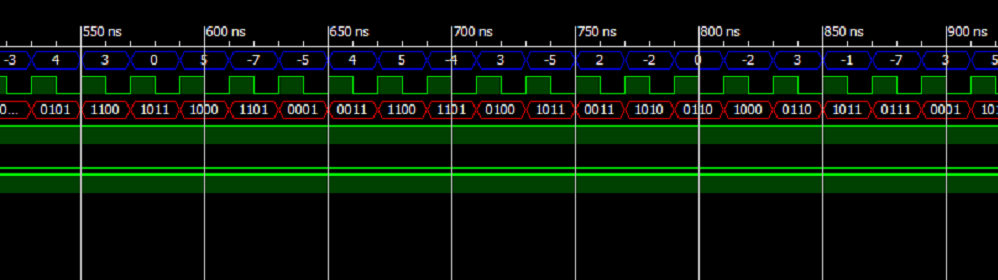

Example 2:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity MasterSlaveDL is

Port ( Din : in STD_LOGIC;

clock : in STD_LOGIC;

Q_m : out STD_LOGIC;

Q_n_m : out STD_LOGIC);

end MasterSlaveDL;

architecture MasterSlaveDL_arch of MasterSlaveDL is

-- dlatch declaration --

component D_Latch is

GENERIC (DELAY : time :=2 ns);

Port ( Din : in STD_LOGIC;

clock : in STD_LOGIC;

Q : out STD_LOGIC;

Q_n : out STD_LOGIC);

end component D_Latch;

-- dlatch declaration --

-- Not Gate declaration --

component NotGate is

Port ( a : in STD_LOGIC;

f : out STD_LOGIC);

end component NotGate;

-- Not Gate declaration --

-- intermediate signals --

signal Q_s : STD_LOGIC;

signal Q_n_s : STD_LOGIC;

signal clockInv : STD_LOGIC;

-- intermediate signals --

begin

L2_inv : NotGate PORT MAP (clock,clockInv);

L1_slave : D_Latch GENERIC MAP(0 ns)

PORT MAP (Din,clock,Q_s,Q_n_s);

L3_master : D_Latch GENERIC MAP(0 ns)

PORT MAP (Q_s,clockInv,Q_m,Q_n_m);

end MasterSlaveDL_arch;